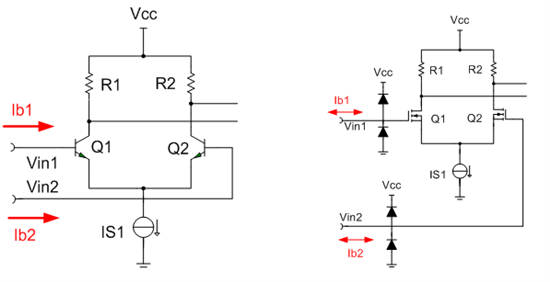

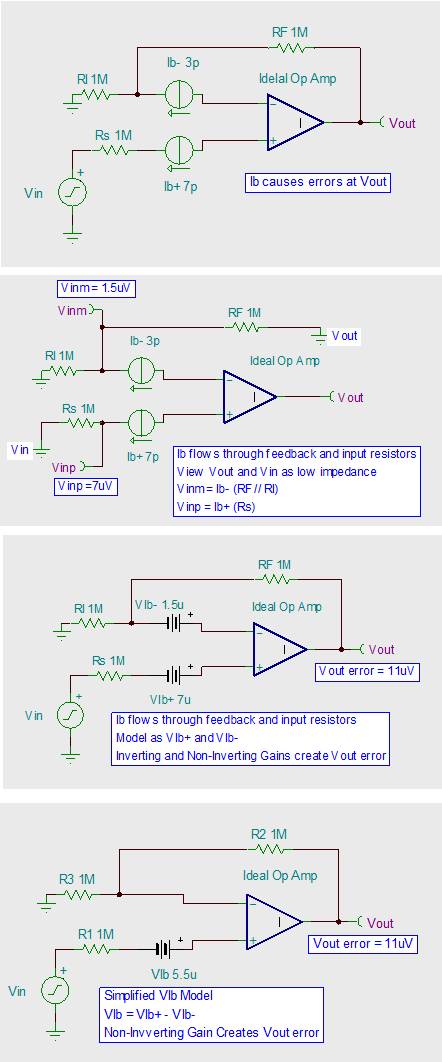

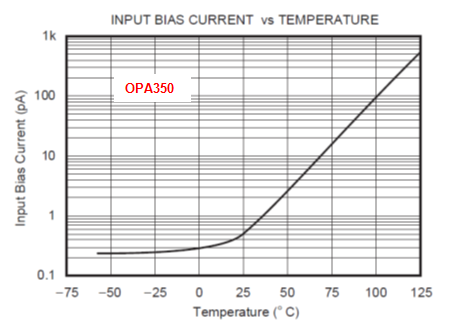

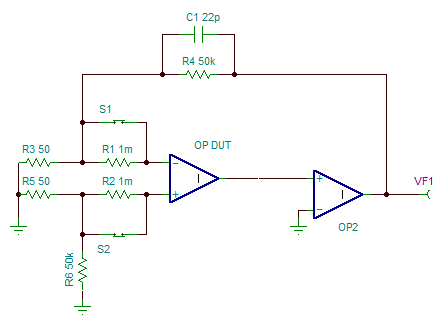

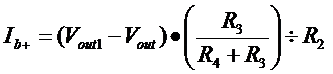

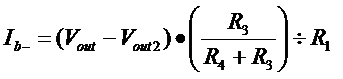

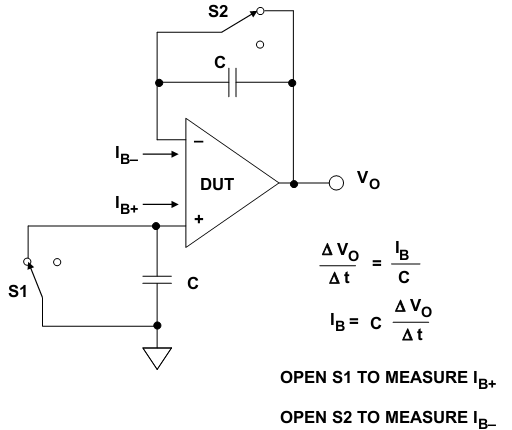

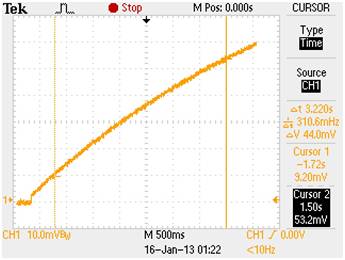

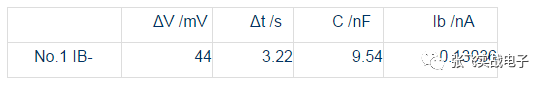

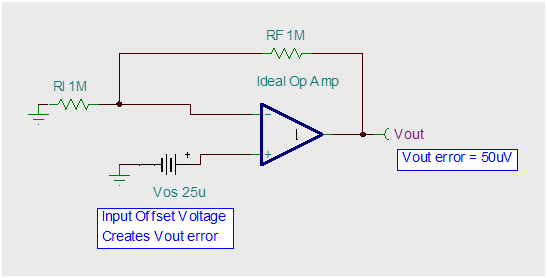

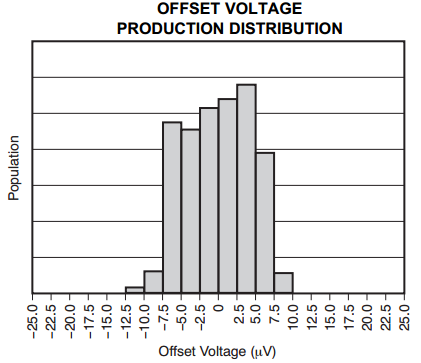

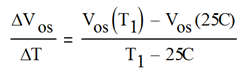

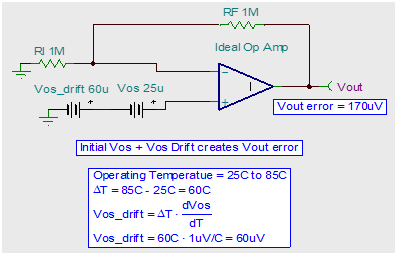

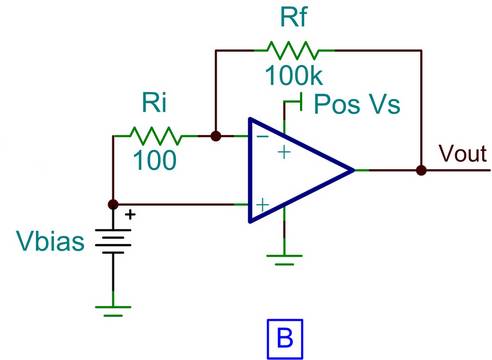

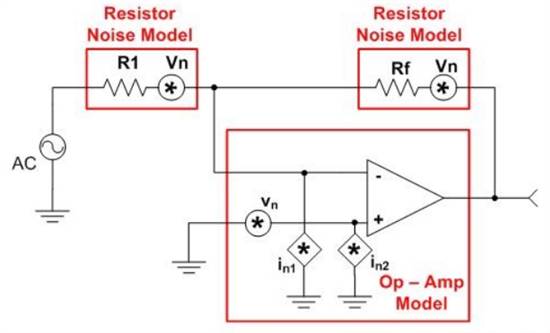

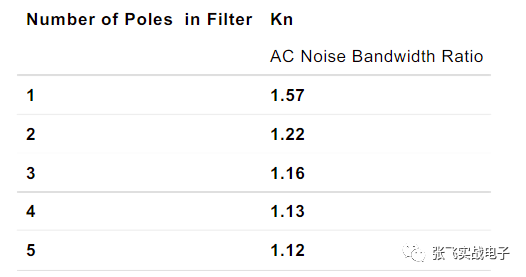

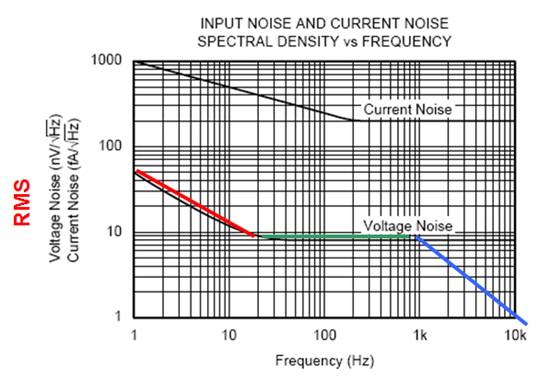

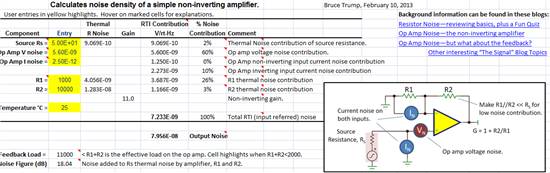

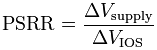

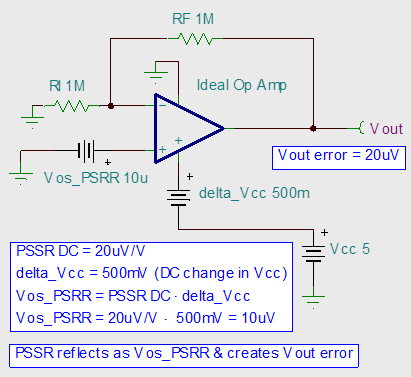

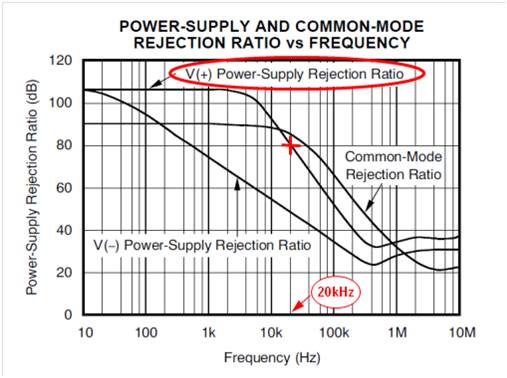

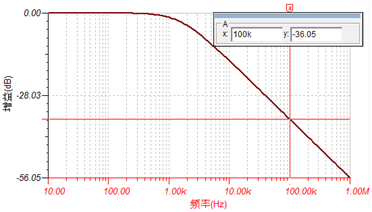

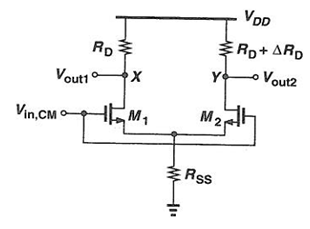

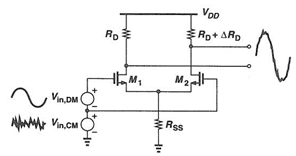

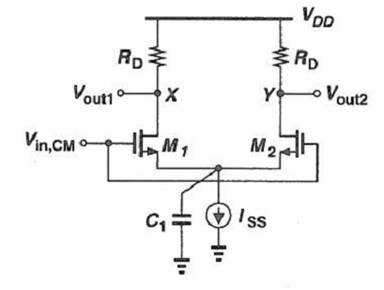

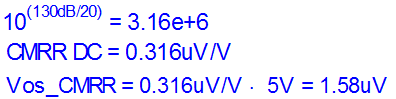

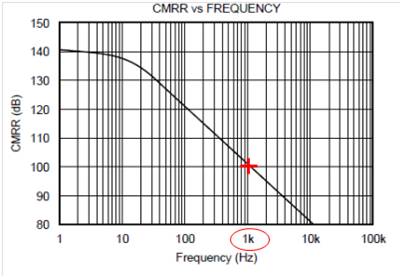

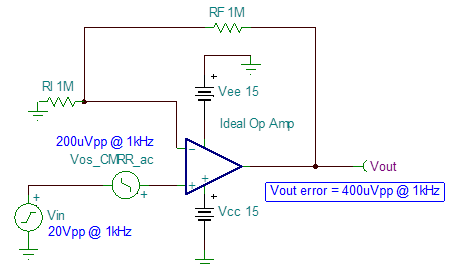

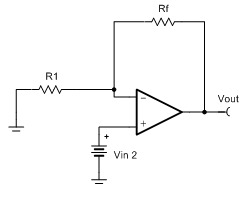

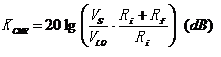

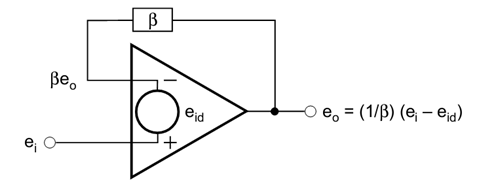

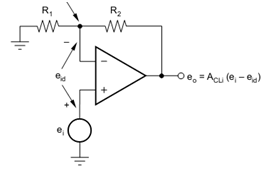

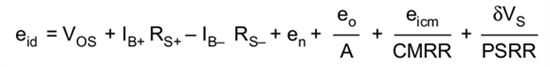

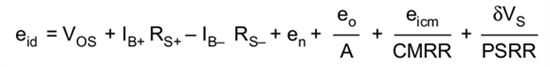

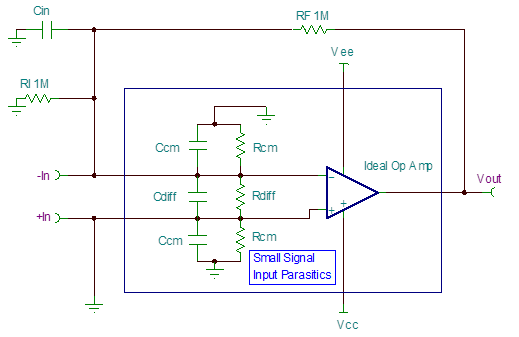

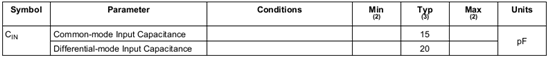

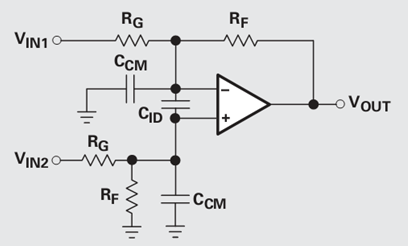

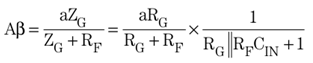

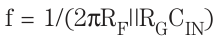

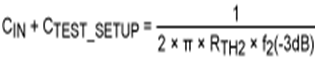

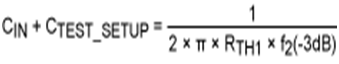

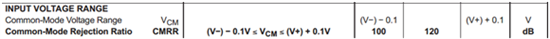

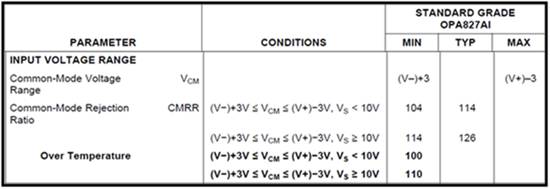

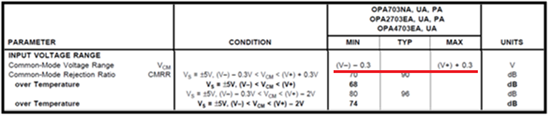

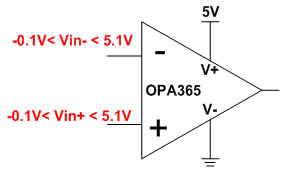

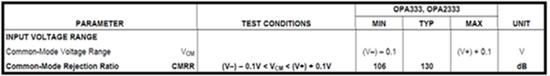

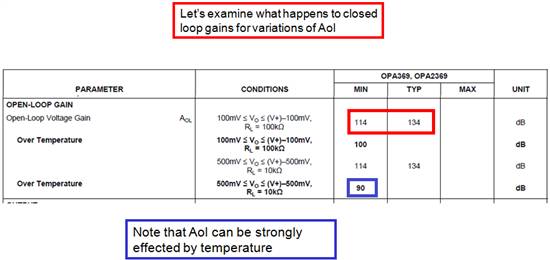

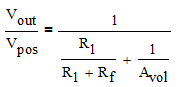

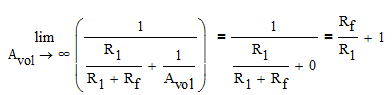

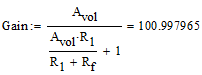

The first section describes the op amp's input bias current Ib and the input offset current Ios. It is well known that the ideal op amp has no input bias current Ib and input offset current Ios. But each actual op amp will have an input bias current Ib and an input offset current Ios. We can use the model in the figure below to illustrate their definition. The input bias current Ib is due to the presence of leakage current (which we will call leakage current) at both input poles of the op amp. We can understand that the input terminals of the ideal op amp are connected in series with a current source, and the current values ​​of the two current sources are generally different. That is to say, in actual operation, there will be current flowing into or out of the input of the op amp (not the same as the virtual amp of the ideal op amp). Then the input bias current defines the average of these two currents, which is well understood. The input offset current is defined as the difference between the two currents. After the definition, let's take a look at the source of this current. Then we have to look at the input stage that is shipped in. The input stage of the op amp typically uses a differential input (voltage feedback op amp). The tube used is either a bipolar bipolar or a FET FET. As shown in the figure below, for bipolar, to make it work in the linear region, it is necessary to provide a bias voltage to the base, or to have a relatively large base current. It is also said that the triode is a current control device. Then the bias current is derived from the base current of the triode in the input stage. Since it is difficult to completely match the two tubes in the process, the base currents of the two tubes Q1 and Q2 always have such a difference. That is the input offset current. The two values ​​of the oppolar input op amp are still considerable, that is to say, they are relatively large, and have to be considered when designing the circuit. For the FET input op amp, because it is a voltage-controlled current device, it can be said that its gate current is very small, usually in the fA level, but unfortunately, each of its input pins has a Protection diode for ESD. Both of these diodes have leakage currents. This leakage current is generally much larger than the gate current of the FET, which is also the source of the bias current for the FET input op amp. Of course, the two pairs of ESD protection diodes are not completely identical, so there are different leakage currents, and the difference between the leakage currents constitutes the main component of the input offset current. The table above is the input bias current and input offset current of the bipolar LM741. This current flows to the external resistor. Even if it is K-class, it will generate an offset voltage of several tens of uV. After amplification, it is easy to Will cause the output voltage error to mV level. The following table shows the input bias current and input offset current of the CMOSFET's OPA369. These two values ​​are much smaller. The better value of the better COMS op amp input bias current and input offset current can be less than 1pA. aims. It is also emphasized here that the reverse leakage current of the ESD is related to its reverse voltage. Therefore, when Vin=(Vcc-Vss)/2, the voltage applied to the two ESD protection diodes is equivalent, and their reverse currents can be considered to be approximately equal. Ideally, no current flows in or out. Is the current reaches a minimum. Therefore, there is a minimum bias current. When the voltage at the input of the op amp is not equal to (Vcc-Vss)/2, it will inevitably cause the reverse voltage of one diode to be high and the other to be low. The current is not equal, and this difference current constitutes the main component of the input bias current. This scene is called the collar effect. Therefore, to minimize the FET input bias current, set the common-mode voltage to (Vcc-Vss)/2. The definitions and sources are analyzed above. Let's talk about the influence of these two parameters on the circuit. The input bias current will flow through the external resistor network, which will be converted into the offset voltage of the op amp. After the operation, it will reach the output of the operation. The input error of the op amp is caused. This also explains why, in the reverse amplifier circuit, why a resistor is connected to the non-inverting input of the op amp. And this resistance should be equal to the value of the reverse input and the feedback resistor in parallel. This is to make the two input terminals bias current flow through the resistor, the voltage values ​​are equal, so that they introduce an offset voltage of zero. To put it this way, it is too abstract, but it is easy to understand some of the following diagrams. Another point is that for the circuit of small current detection, it is generally a transimpedance amplifying circuit, such as a photodiode detecting circuit. Generally, the optical power signal which is relatively weakly converted by the optical signal is weaker, and is often nA level rather than pA level. The intention of this circuit is to let the photocurrent flow to the feedback resistor to generate a voltage at the output of the amplifier circuit. If the op amp's input bias current is too large, just a portion of this faint photo current will flow into the op amp's input without a preset I/V linear conversion. Also note that many of the op amp's input offset currents vary with temperature. As shown in the figure below, the OPAl350's input offset current rises rapidly above 25 degrees. The input bias current at 100 degrees is several hundred times that of 25 degrees. If the system is designed to operate over a wide temperature range, this factor has to be considered. The above mentioned the input bias current and offset current of the op amp, I hope to be useful to everyone. The other parameters are detailed in the next section. The previous section talked about the op amp input bias current and input offset current. This section gives an input bias current measurement method. In general, there are two main test methods. One is to let the input bias current flow into a large resistor to form an offset voltage, then amplify the offset voltage and measure it, so that the input bias can be calculated backwards. The method is to let the input bias current flow into a capacitor, and integrate this current with a capacitor, so that the bias current of the op amp can be calculated by measuring the rate of change of the voltage across the capacitor. First introduce the first method, the specific circuit is shown below, C1 is the lead compensation capacitor to prevent the circuit from oscillating, according to the actual circuit selection. The OP2 is a test-assisted op amp that requires an op amp with low bias voltage and low bias current. Test steps and principles are calculated step by step. (1) First test the offset voltage of the op amp. Turn off S1 and S2 and test the output voltage of the OP2 op amp to record Vout. Then the input offset voltage is: (2) Turn on S2, Ib+ of the op amp to be tested flows into R2, an additional offset voltage Vos1 is formed, and the output voltage of the OP2 op amp is tested to record Vout1. Then the op amp input offset voltage is: (2) Turn off S2, turn on S1, Ib- of the op amp to be tested flows into R1, an additional offset voltage Vos2 is formed, and the output voltage of the OP2 op amp is tested to record Vout2. The op amp reverse input offset voltage is: (4) The op amp input bias current is Ib=[(Ib+)+(Ib-)]/2 The op amp input offset current is Ios=(Ib+)-(Ib-) This test method has several drawbacks. One is the use of large resistors R1 and R2, which are typically M-ohms, which introduce large voltage noise. Limited by the resistance of resistors R1 and R2, it is difficult to measure the bias current of the FET input op amp. The second method of testing is to let the input bias current of the op amp flow into the capacitor. The specific test is shown below. The principle of the test is easily understood from the formula in the figure. The key to this test is to select a capacitor with a very small leakage current. (1) Turn on S1, IB+ flows into capacitor C, and observe the change of Vo with an oscilloscope. The result is as shown below. According to the above method, IB+ can be calculated. (2) Turn off S1 to turn on S2, IB- into capacitor C, and observe the change of Vo with an oscilloscope. As a result, as shown below, IB- can be calculated. (3) The input bias current and offset current of the op amp can be calculated according to the definition. This test method can measure the offset current of the fA level. Low leakage current capacitors are required for testing. Teflon capacitors, polypropylene (PP) capacitors or polystyrene capacitors with very low leakage current are recommended. Another experience is shared. In the soldering process, the leakage current of the FET op amp is greatly increased due to impurities such as solder paste remaining on the pins. I have tested an op amp with a bias current of less than 10pA. Since there is no cleaning of the pin, the result is a large error, or error, which is up to the level of nA. In the application of the op amp, the input offset voltage Vos problem of the op amp is inevitably encountered. Especially when the DC signal is amplified, due to the presence of the input offset voltage Vos, the output of the amplifier circuit always superimposes what we do not expect. error. For a simple, old-fashioned, classic example, due to the presence of the input offset voltage, our electronic scale will have a weight display when it has not been adjusted. We don't always hope that the weight we buy is different from the actual one. It is almost nothing to buy an apple. If you buy a platinum ring, you can get a lot of money. The following describes the offset voltage of the op amp and its calculations. Finally, introduce some low input offset voltage op amps. Inadequacies, a lot of bricks. Ideally, when the input voltages of the two inputs of the op amp are the same, the output voltage of the op amp should be 0V, but the actual situation is that even if the voltages of the two inputs are the same, the amplifier circuit will have a small voltage output. As shown below, this is caused by the input offset voltage of the op amp. Of course, the strict definition should be that in order to make the output voltage of the op amp equal to 0, it is necessary to add a small voltage to the two inputs of the op amp. The small voltage that needs to be added is the input offset voltage Vos. Note that the output offset voltage is added to the output voltage instead of the input voltage, and the output offset voltage is divided by the gain (small difference). The input offset voltage of the op amp is derived from the mismatch between the two tubes of the differential input stage of the op amp. As shown below. This mismatch is inevitable due to process level limitations. The mismatch of the differential input stage is a bad boy, and it will cause many other problems, which will be introduced later. I have consulted a senior op amp design engineer. According to him, the matching degree of the two pipes is proportional to the square root of the area of ​​the pipe within a certain range, that is, the matching degree is increased by twice. The area has to be increased by four times. When it reaches a level, even if the area is increased, the matching will not be improved. Increasing the area is to increase the cost of the IC. There is a commonly used method, which is to test after the op amp is produced, and then Trim (can be understood as tuning). This will increase the accuracy of the op amp. Of course, both testing and Trim cost. Therefore, the price of precision op amps is relatively expensive. This is only a chat, hehe. We focus on the input offset voltage because it introduces errors into the amplifier circuit. The following is an analysis of the error it brings. Before the calculation, we will recognize a parameter that makes us not too cool, the temperature drift of the offset voltage, that is, the input offset voltage mentioned above will change with the temperature. And the temperature of the application environment of our actual circuit always changes, which brings us a tough problem. The table below shows the parameters taken on the OPA376 datasheet. It has a maximum temperature drift of 1uV/°C (-40°Cto 85°C). The Vos of a large number of op amps are normally distributed, so the datasheet will generally give a histogram of the offset distribution. When the temperature changes, the input offset voltage temperature drift is defined as: Another important parameter that has just been forgotten is the long-term drift of the op amp input offset voltage , which is usually given like uV/1000hours or uV/moth. Some datasheets will give this parameter. The following example calculates the maximum offset voltage of the OPA376 at 85 °C, mainly in two parts, one is the input offset voltage at 25 degrees, and the other is the offset voltage drift caused by temperature changes. The specific steps are as follows. From the results, it seems that 1uV/°C temperature drift is the dominant error when multiplying the temperature change. Therefore, if the circuit is designed to be used over a wide temperature range, special attention should be paid to temperature drift. Vos (85 ° C) = 25uV + 60uV = 85uV. If the Gain of the amplifier circuit is changed to 100, the maximum output offset voltage is 8.5mV. This is the worst case. The test on the input offset voltage is described in "Detailed Explanation and Analysis of Op Amps Parameters - part2, How to Measure Input Bias Current Ib, Offset Current Ios". If you are interested, you can check it out. There are also simple test methods, as shown below: Vos = Vout/1001 Need to be reminded that when using an easy method to test the input offset voltage of a single-supply op amp, you need to short the input and provide a low-noise, stable voltage bias. As shown below. Below are some low temperature drift amplifiers with a maximum drift of only 0.05uV/°C. The input offset voltage Vio has a maximum value of only 5uV. This article is not about the noise theory of op amps. TI's senior application manager Art Kay has written a series of articles to analyze the noise of op amps. I believe most analog circuit engineers have read them. There are engineers in China who translate it into Chinese. Today, I mainly analyze the noise composition of the op amp circuit from the top-down perspective. The main points of the calculation are the main points and the most interesting place. The most important thing is to provide you with a convenient calculation tool. It is very easy to use and let the noise The calculation becomes simple. In the reverse amplification circuit composed of op amps, the noise mainly comes from three aspects. (1) The input noise voltage of the op amp en (data and curve in the datasheet) (2) The input current noise of the op amp in (data and curves can also be found in the datasheet). This needs to flow through the resistor and convert it into voltage noise. (3) Setting the thermal noise of the resistors R1 and Rf of the amplification factor, that is, can be calculated by the classical formula. Noise = √ (4kTKRΔf). This is inevitable. In many cases it will be the main source of noise. The calculation of the op amp noise is to find these three values ​​one by one, since these noises are irrelevant. Their vector sum is the total input noise of the op amp. Then multiply the noise gain to get the output noise, the formula is as follows. It seems to be simple and it is very troublesome. We add the calculated and input total noise to the positive input of the ideal op amp to get the noise model of the op amp. Note that it is the positive input terminal, so the gain of the noise is G=1+Rf/R1 regardless of the same-direction amplifying circuit or the inverse amplifying circuit. We can simply understand that noise is a signal that is superimposed on the input of the op amp. As shown below The above mentioned an important issue, the noise gain of the op amp. An important issue is also the noise bandwidth of the op amp. The op amp noise parameters given in the datasheet are generally spectral density values ​​such as 1.1 nV √ Hz. That is to say, it is necessary to integrate it in the noise bandwidth to obtain the RMS voltage value of the noise. The noise bandwidth is different from the -3dB bandwidth of the signal. Specifically, the bandwidth of the Brickwall filter. To put it simply, the actual filter response curve is converted to the bandwidth of the rational low-pass filter when the area is guaranteed to be constant. Fortunately, we can look up the table, the -3dB bandwidth of the N-order filter and the bandwidth conversion factor of the Brickwall filter. As shown in the table below It seems to be troublesome, don't worry, and the more troublesome thing is that the op amp's input voltage noise and input current noise are frequency dependent. At very low frequencies (0.1Hz-10Hz), it is mainly 1/f noise. In the future, it is mainly white noise, as shown below. It needs to be segmented into points. The following figure shows the calculation of the noise voltage. As long as the value of 1/f noise at a specific frequency and the value of flat noise are input, the noise density at different frequencies can be calculated. By inputting the start and stop frequency of the frequency band, the punctuality rate of each noise in the lower frequency band can be analyzed. The figure below is a method to calculate the noise density of the same-direction amplifier circuit (take OPA627 as an example). You only need to input the signal source resistance, op amp voltage noise, op amp current noise, resistance value and temperature to calculate the noise of the output circuit. Density, which greatly increases the computational efficiency. The calculation results also give the punctuality rate of each noise source, which is convenient for us to optimize the noise. This section talks about the power supply rejection ratio of the op amp. In an ideal op amp, the characteristics of the op amp do not change as the supply voltage changes. Of course, when analyzing an ideal op amp, the power supply we use will also be assumed to be an ideal power source. However, this is not the case. Actual op amps will always cause changes in the op amp parameters when the power supply voltage changes. This leads to an important parameter of the op amp, the op amp's power supply rejection ratio PSRR. The detailed definition of PSRR is given in Wikipedia. When the power supply voltage of the op amp changes, it will cause the change of the input offset voltage of the op amp (and the offset voltage). The ratio of these two changes is the op amp. PSRR. As follows Usually expressed in dB. PSRR = 20log (⊿Vcc/⊿Vios). In some data sheets, the ratio of the offset voltage to the power supply change is also indicated. The unit is generally uV/V. As shown in the figure below, it is a representation in the datasheet of OPA365 . This is not difficult to understand. We don't have to be sad to find the ratio dB value defined by the above formula. Both of these representations allow us to clearly understand the op amp's ability to suppress supply voltage variations. The reason why the PSSR is a finite value is also due to an incomplete matching of the op amp differential input transistors. The following focuses on its impact. The following figure is a calculation example for the OPA376 op amp. When the power supply voltage changes by 500mV, it will cause a change in the input offset voltage of 10uV. If the amplification factor is 2, the output will change to 20uV. Some circuits have a larger amplification factor, and the output offset voltage changes greatly. This is enough to cause an error in the signal delivered to the 16bits ADC. (The change in one LSB of a 16-bit ADC is 15 ppm of FSR). The DC power supply rejection ratio is discussed in the previous section. In the actual application circuit, the power supply voltage of the op amp may be constant. Let's analyze another key parameter, the op amp AC power supply rejection ratio AC-PSRR. This parameter is more valuable than the actual application circuit, but it is often overlooked. The DC PSRR is often given in the datasheet parameter table of the op amp. AC-PSRR is often given in the form of a chart, and we often ignore the information in the chart. However, what we ignore is often the key. The following figure shows the PSRR chart in the datasheet of the OPA376. From the chart we can see two pieces of information: (1) PSRR decreases with the increase of the AC frequency of the power supply, and (2) The AC-PSRR of the positive and negative power supplies is different. The above two points will cause unpleasant problems in the application circuit. The following figure shows a peak-to-peak value of 100mV on the power supply and a ripple of 20kHz, which will increase the output of the amplifier circuit by 20uV, 20kHz. Noise signal. As mentioned above, when the op amp is powered by a switching power supply, the PSRR drops as the frequency increases. This causes a large ripple noise at the output. The following provides an easy way to work only with low power op amps. Add a small resistor between the DC-DC output power supply and the op amp's power supply (as shown below) if the op amp's power consumption is less than 5mA. Then this 10 ohm resistor produces a voltage drop of less than 50 mV. Let's take a look at the effect of this circuit. The frequency response is -36dB at 100kHz, which is equivalent to a 36dB PSRR for the op amp. This power loss is worthwhile in exchange for this effect. Another effective method is to filter the core capacitor to the power supply. The core capacitor is a three-terminal capacitor, but compared with the conventional three-terminal capacitor, since it is directly mounted on the metal panel, its grounding inductance is more Small, almost no lead inductance, in addition, its input and output are separated by a metal plate, eliminating high frequency coupling, these two characteristics determine the filter capacitance of the feedthrough capacitor close to the ideal capacitance. For the core capacitance, you can refer to the relevant information if you are interested. The common analog ratio of op amps is an op amp parameter that is often of interest to everyone, especially in differential amplifiers and instrumentation amplifiers. However, this section only discusses the common mode rejection ratio of the op amp and the error that the CMRR brings to the op amp. The differential amplifiers and instrumentation amplifiers are discussed later. Before we start to discuss the common mode rejection ratio of the op amp, let's first understand the common mode input voltage of the op amp. The common mode input voltage of the op amp refers to the average of the voltages of the two input pins of the op amp. Note that the average is "This is very important, as shown below. For op amps with bipolar input stages, the op amp's common-mode input voltage typically does not reach the power rail. Some rail to rail input op amps have a common mode voltage that can reach the power rail. In an ideal op amp, the op amp's differential mode amplification is infinite and the common mode amplification is zero. The ideal is always beautiful, and the reality is always cruel. Therefore, the actual op amp is not the case, the differential amplifier magnification of the actual op amp will not be infinite, and the common mode amplification factor will not be zero. We thus define the common mode rejection ratio (CMRR) of the op amp, the ratio of the differential mode gain to the common mode gain, as follows Another parameter is very common, which is CMR, which is actually a logarithmic representation of CMRR, as follows: However, these two parameters are often mixed. As long as we understand that they are all saying that the op amp can suppress the common mode signal. The op amp only amplifies the common mode signal. Of course, this is not what we expect, but it is inevitable. Mainly from the following reasons: (1) The mismatch between the op amp and the input stage. This can be further divided into the following causes: 1) The source or drain resistance does not match, 2) Signal source resistance 3) junction capacitance between gate and drain 4) Forward transconductance mismatch 5) Gate leakage current (2) Output impedance of the trailing current source (3) The parasitic capacitance of the trailing current source changes with frequency. Let's take a look at a few of the above reasons to see their impact: (1) The resistance mismatch, as shown in the figure below, due to the resistance mismatch, a common mode voltage change ΔVin will be converted to a differential mode voltage at the X and Y points. Calculated as follows, this differential mode signal introduced by the mismatch resistance ΔRd is converted into noise of the differential stage output signal. (2) The mismatch of the input transistors and the mismatch of the tubes will cause a slight difference in the current between the two tubes, and the transconductance of the two is different. Due to the mismatch of the input stage tubes, the common mode signal is converted into a differential mode error, which can be expressed by the following equation, which represents the CMRR caused by the mismatched transconductance. (3) Another reason is that the parasitic capacitance of the trailing constant current source changes with frequency. This causes a change in the current of this constant current source. The purpose of replacing the emitter or source resistance of the differential input with a constant current source is to keep the current constant and high impedance. However, if its current changes with frequency, it will inevitably reduce the common mode rejection of the differential input. The previous section briefly introduced the definition of the common mode rejection ratio and the cause of it. Let's introduce it, its impact. The purpose of this series of posts is to clearly define the definition of the op amp parameters, analyze the cause of the problem, introduce the impact of this parameter on the circuit, and finally try to introduce some empirical methods to reduce and avoid these effects as much as possible. In simple terms, CMRR is a DC precision parameter of the op amp. It is good or bad, which will cause the output error of the amplifier's amplifier circuit to be good or bad. The following table shows the common mode rejection ratio CMRR indicated in the data sheet of the OPA177. Note that the value calibrated in the table refers to the DC common mode rejection ratio in the input common mode voltage range. Its minimum value is 130dB, which is a very high value. Since the CMRR is finite, when the op amp input has a common mode voltage of Vcm, it introduces an input offset voltage, which we call Vos_CMRR. As shown below When the common mode voltage is 5V, this offset voltage is 1.58uV. The calculation process is as follows, the DC common mode rejection ratio is converted into a ratio of: For the circuit with G=2 in the above figure, the output error is 3.16uV. For the 2.5V reference source, the bipolar input 24-bit ADC is equivalent to the DC error of 11 LSBs, which directly affects the accuracy of the last four bits. Another bad effect is described below. The CMRR of the op amp is reduced as the frequency increases. A graph is usually given in the Datasheet to indicate this change. As shown below, this is a very unpleasant feature. We can calculate the effect of this feature, as shown in the figure below, when the common mode signal is a 20Vpp@1KHz sinusoidal signal, it will introduce an input loss voltage of Vos_CMRR_AC=200uV@1kHz. For a Gain=2 amplifier circuit, its input error signal will be 400uV@1kHz. One thing that needs attention is that for the reverse proportional amplification circuit, as shown in the following figure, its codirectional end is connected to the ground due to "virtual short". The common mode signal of this amplifier will be 0 and will not change as the signal changes. Therefore, the error caused by the common mode signal is small. For the same-direction proportional amplifying circuit, as shown in the following figure, its co-directional terminal is a signal that is connected, due to "virtual short". The common mode voltage of this amplifier is the voltage of the signal. If the signal itself is a very high frequency signal, the amplitude is also large. Then the Vos_CMRR_AC introduced by this signal will be very large. In this case, an op amp with a high CMRR at the signal frequency should be used. After the above analysis, even then, the impact of Vos_CMRR_AC may be very serious. Finally, a brief introduction to the CMRR test of the op amp, usually people will think of the method of the following figure to test CMRR, this method seems simple, but there is a big problem, that is, it requires a very high resistance matching An op amp with a CMRR >100dB is required and requires a resistance of less than 1ppm. This is almost impractical. The easy way is the way below. It requires much lower matching of resistors. Set the output voltage of the signal source to VS, and measure the output voltage of the auxiliary op amp to be VL0.   The main DC parameters of the op amp are analyzed in detail in the previous section. The reason we analyze them is that they introduce DC errors into our circuits. The main purpose of this sticker is to find out the causes that affect the DC error of the op amp and how it affects it. So that engineers pay more attention when designing precision amplifier circuits. Let us first look at the theoretical model of the amplifier circuit, as shown below. This circuit can no longer be seen in the application circuit of the op amp. Its output is eo. Equal to the closed loop gain (1/β) multiplied by the input signal, here. We have to pay more attention to the input signal, which is composed of the input signal ei of the circuit minus the error eid introduced by the op amp. Where β is the feedback coefficient, and for a typical isotropic amplifier circuit like the one below, its value is R1/(R1+R2). This is described in detail in the model textbook, but it is awkward. This article is more about eid. For eid, our first reaction may be the input offset voltage offset, and the further reaction is the input bias current flowing through the resistor network to cause the error voltage. But it is true that there are not only these two factors, but also the seven aunts and the eight aunts who come together to join in the fun. Then we will show its true face: There are enough items on the right side of the upper equal sign. Really did not let us down, so many parameters, involved in the production of DC error ranks. Of course, these parameters, that is, the parameters mentioned in part1-part8. Let's take a closer look at the formula mentioned in the previous section: Let's take a look at them one by one. (1) Vos, input offset voltage, everyone is familiar, not much nonsense. The worse thing is that it is not a value that is honest, it will drift with temperature. (2) Ib+, the non-inverting input bias current, which flows through the equivalent impedance of the same direction to form an error voltage. (3) Ib-, the inverting input bias current, which flows through the opposite end equivalent impedance to form an error voltage. Some people may have noticed how the input impedance is calculated. The following figure will understand. In short, the input resistance (source resistance plus input resistance) is connected in parallel with the feedback resistor. Don't forget the source resistance, because we often use high-impedance sensors as the source. (4) en, equivalent input noise. This value, my understanding is not only the en given in the datasheet such as 1.1nV √ Hz. It is integrated with the contribution of voltage noise, current noise and resistance noise. Is the value of all noise equivalent to the input. Please refer to Art Kay's article and part4 of this series of blog posts. (5) eo/A, this expression may have been noticed by many people. The reason for this is that the open loop gain A of the op amp is not zero. This is because the input input value is different, and the equivalent input error is different. For example, if the output value is 5V. The open loop gain is 100dB, not too low. Its conversion to the input error is 50uV. Not a small amount. (6) eicm/CMRR, needless to say, the same mode voltage at the input is divided by the common mode rejection ratio. Another disadvantage is that the CMRR of the op amp drops as the frequency of the common mode signal increases. The CMRR of many op amps is tens of dB lower than DC when the common mode signal is above 10KHz. (7) ΔVs/PSRR, error introduced by the change of the power supply voltage. Similarly, the AC PSRR decreases as it increases with frequency. After reading this, you may think that this small error is drizzling, up to mV level, even at uV level, don't forget, it is also multiplied by a gain Gain. If the input error is 100uV. When the gain is 100 times, the error signal output is 10mV. Input_error x Gain = Output Error If you still feel nothing, then let's talk about an experience value. A 16-bit ADC with a full-scale 5V ADC has an LSB of about 75uV. As long as the 75uV error causes a one-bit change in the ADC. If the output error signal of the amplifying circuit is 1mV, this signal is directly applied to the ADC, and the error directly caused is 13 LSB or more. This Output error is really mixed. There is a DC component, which can be removed by ADC sampling and correction. There are noisy signals and there are components of communication. The least expected, it will drift with temperature. In the design circuit, we can find out the main factors causing DC error through the above analysis, and then try to reduce it. The image below illustrates the characteristics of the impedance of the input of the op amp. There are two main parameters, input impedance and input capacitance. For voltage feedback type of input, the input impedance is mainly determined by the input stage, which is generally the operational amplifier of the BJT input stage. The common mode input impedance will be greater than 40MΩ. The differential mode input impedance is greater than 200GΩ. For op amps in JFET and CMOS input stages, the input impedance is much larger. This impedance is usually expressed as resistive. As common sense is known to us. What deserves more attention is the input capacitance of the op amp. This parameter is usually listed in the table of the datasheet, but is often overlooked. The input capacitance of the op amp is usually divided into a common mode input capacitor Ccm and a differential mode input capacitor Cdiff. As shown below is the input capacitance listed in the OPA376 datasheet. For op amps with EMI suppression characteristics, such as the LMV832, its input capacitance will be designed to be larger. Below is the input capacitance value of the LMV832 with EMI suppression. The op amp's input common-mode capacitor Ccm and differential-mode capacitor Cdiff form the op amp's input capacitor Cin. In many applications, the op amp's input capacitance is not a problem. However, in some applications, the amplification circuit is unstable. In particular, the capacitance of the inverting input is one of the major culprit in the instability of the amplifier circuit. As shown in the figure below, the model is placed under the influence of input capacitance. This reverse input capacitor introduces a pole into the loop gain of the op amp. It is the existence of this pole that may cause instability of the amplification circuit under certain conditions. The poles introduced by the op amp input capacitor are as follows. Even if this pole 0-dB crossover is within the frequency, but very close to the 0-dB crossover frequency, it can also cause problems. At the frequency point of this pole, the phase has a phase delay of 45 degrees, which is likely to reduce the phase margin of the amplifying circuit. For example, the 0-dB crossover frequency of the amplifying circuit is 2 MHz. The phase margin at 2 MHz is 89°. If the frequency point of this pole is also at 2MHz, it will reduce the phase margin by 45°. It becomes φ = 89° – 45° = 44°. The 44 degree phase margin is not enough. Usually, the input capacitance of the amplifier circuit is not only composed of the input capacitance of the op amp, but also the stray capacitance and pin capacitance caused by the wiring. External stray capacitance at the inverting input of the op amp should be avoided as much as possible, especially in high speed applications. The ground plane should be removed from the area around the inverting input to minimize stray capacitance on the PC board. In addition, all connections to this pin should be as short as possible. In some applications, feedback capacitors are often added to increase the stability of the amplifier circuit. The loop gain of the circuit after adding the feedback capacitor is, and the visible feedback compensation capacitor introduces a zero point into the loop gain. Normally we can get the op amp's input capacitance Ccm and Cdif in the op amp's datasheet. These values ​​are usually typical. In some cases, it may be necessary to measure the input capacitance of the op amp. A practical test method is provided below. The following figure is the schematic diagram of the test. The basic test principle is to connect the operational amplifier into a follower, and then connect a resistor in series with the input of the same direction (the resistance is generally between 100K-1M). The input capacitance of this resistor and the op amp will be To form an RC circuit, we tested the -3dB frequency of this circuit, known as series resistance. It is possible to calculate the input capacitance of the op amp. It should be noted here that the resistor also has an equivalent shunt capacitance. The equivalent parallel capacitance of a typical 1/4W capacitor is approximately 0.3pF. We can reduce the equivalent parallel capacitance of the resistor by means of series resistors. The image below is the actual test setup. The instruments used are network analyzers, high impedance FET probes. And power splitter. Why not use an oscilloscope? This is for a reason. Since the input capacitance of the op amp is usually less than 10pF. The capacitance of the oscilloscope's probe is usually around 10pF. If you use an oscilloscope probe to measure the input capacitance of an op amp, you can't measure it at all. Therefore, high-impedance FET probes such as Tektronix® P6245 with a capacitance of less than 1pF are required. Here's a brief introduction to the test method: (1) First, test the stray capacitance of the PCB when the op amp is not installed. The test result of the network analyzer reads the -3d frequency point f1. And calculate the stray capacitance: (2) Install the op amp in the circuit, and then test the -3dB frequency point f2 with the network analyzer. And calculate the sum of the op amp input capacitance and stray capacitance: (3) If the series resistance we choose is much smaller than the common mode resistance of the op amp, it can be regarded as Rth1=Rth2. Then the above formula can be written as: In this way, by calculating the difference, the input capacitance of the op amp can be calculated. With the widespread use of single-supply op amps, the rail-to-rail input of the op amp becomes a buzzword. Most low voltage single-supply op amps are now rail-to-rail inputs. Let me talk about two nonsense and explain the rail-to-rail. The rail here refers to the power rail. The two power supply voltages of the op amp are +/-15V. These two supply voltages limit the input and output signals of the op amp just like two parallel "tracks" with a distance of 30V. The rail-to-rail input of the op amp means that the signal voltage at the input of the op amp can reach the two rails of the power supply and remain undistorted. For example, the input signal voltage can reach +/-15V. The op amp's input voltage range can be found in the op amp's datasheet. It is the Common-Mode Voltage Range (Vcm). The following table shows the input voltage range of the OPA365. It can be seen that it is a typical rail-to-rail input op amp. A typical BJT and JFET are non-rail-to-rail input op amps. The OPA827 common-mode input voltage range is (V-) + 3V to (V+) - 3V, as shown in the following table, typical non-rail-to-rail op amps. Single-supply (we call it "single-supply" for a while) The input stage of an op amp typically has three configurations. The first is to use PMOS as the differential input stage. Such an input input stage voltage can be lower than the negative supply rail by 0.2 or even 0.3V, but does not reach the positive supply rail, such as the OPA336. The following table shows the OPA336 input voltage range indicated in the datasheet. Its input stage block diagram is shown below, a typical PMOS differential input stage. Since the input voltage of the PMOS differential input stage cannot reach the positive power rail, the input voltage of the NMOS differential input stage can reach the positive power rail, but the negative power rail is not reached, generally 1.2V on the negative power rail. on. At this point, some people thought of connecting the PMOS and NMOS differential input stages in parallel. The PMOS differential input stage operates near the negative supply rail and operates the NMOS differential input stage as it approaches the positive supply rail. This will not allow the rail-to-rail input of the op amp. It’s too clever. It is true that earlier rail-to-rail input op amps were designed this way. And now this technology is being used in large quantities. The following figure shows the input stage of the OPA703, which is a typical IO and NMOS parallel op amp input stage. When the input common mode voltage is at (Vss-)-0.3V The following table shows the common mode voltage input range (V-) -0.3V to (V+) + 0.3V given in the OPA703 datasheet. Bipolar输入级è¿å…¥åŒæ ·ä¹Ÿæœ‰è¿™æ ·çš„结构,如下图是典型PNP与NPN型三级管并è”å½¢æˆçš„差分输入级。 13ä¸è®²åˆ°äº†å¸¸ç”¨çš„轨至轨è¿æ”¾æ˜¯é‡‡ç”¨NMOS与PMOS差分输入级相并è”的方法。这一方法巧妙的解决了输入信å·è¾¾ä¸åˆ°ä¸¤ä¸ªç”µæºè½¨çš„问题。在当今轨至轨输入的è¿æ”¾ä¸å¾—到广泛的应用。 但是这ç§å¹¶è”差分输入级的è¿æ”¾æœ‰ä¸€ä¸ªå…ˆå¤©çš„问题就是输入失调电压交越问题。如下图所示,为并è”差分输入结构的è¿æ”¾çš„输入å‰çº§ã€‚ 下图是这ç§è¿æ”¾çš„输入失调电压å¯ä»¥çœ‹å‡ºã€‚éšç€å…±æ¨¡ç”µåŽ‹çš„å‡é«˜PMOS在2V(用于举例的值)左å³å°†å…³é—,而NMOSå³å°†æ‰“开,就在这个节骨眼上。è¿æ”¾çš„输入失调电压å˜ç”Ÿäº†è·³å˜ã€‚这个å¯ä»¥ç†è§£ï¼Œä¸¤ç»„ä¸åŒç»“构的输入级的输入失调电压是ä¸åŒçš„,在交接棒时,这个失调电压也完æˆäº†äº¤æŽ¥æ£’。对于直æµä¿¡å·è¿™ä¸ªé—®é¢˜ä¼šå¼•èµ·è¯¯å·®çªå˜ï¼Œå¯¹äºŽæ£å¼¦äº¤æµä¿¡å·ï¼Œè¿™ä¸ªé—®é¢˜ä¼šå¼•èµ·ä¿¡å·çš„失真。在交越点引入一个å°å°çš„å°é˜¶ã€‚ 为了解决这个问题,设计了两ç§é¢†å…ˆçš„差分输入级。第一ç§ç»“构如下图。PMOS差分输入级能达到负电æºè½¨ï¼Œè€Œè¾¾ä¸åˆ°æ£ç”µæºè½¨ï¼Œæ€»æ˜¯å·®è¿™ä¹ˆ1Vå·¦å³å¤Ÿä¸ç€ã€‚我们把输入级的电æºåœ¨å†…部æ高1.8Vã€‚æ°´æ¶¨èˆ¹é«˜ï¼Œè¿™æ ·çš„è¾“å…¥çº§å°±èƒ½è¾¾åˆ°è¿æ”¾çš„æ£ç”µæºè½¨ã€‚由于åªæœ‰ä¸€ç»„差分输入级,并ä¸ä¼šå˜åœ¨è¾“入失调电压交越的问题。 这一技术在TIçš„å•ç”µæºè¿æ”¾OPAl365上得到应用。如下图。 到这并没有结æŸï¼Œå¦ä¸€ç§æŠ€æœ¯åœ¨TIçš„å•ç”µæºè½¨è‡³è½¨è¿æ”¾ä¸å¾—到应用。这就是自调零技术。下图使用了自调零技术(MOSFET Zero Drift)å‰åŽã€‚输入失调电压跳å˜å°±éžå¸¸å°äº†ã€‚ 这一技术在TIçš„OPA333è¿æ”¾ä¸å¾—到应用,下表是OPA333çš„Vcm输入电压范围。 ç†æƒ³è¿æ”¾çš„开环增益Aolæ˜¯æ— ç©·å¤§çš„ã€‚è¿™æ˜¯æˆ‘ä»¬åœ¨æ¨¡ç”µè¯¾æœ¬ä¸Šå¦åˆ°çš„è¿æ”¾çš„一æ¡åŸºæœ¬çŸ¥è¯†ã€‚但现实总是残酷的,残酷到所有的è¿æ”¾çš„开环增益都ä¸æ˜¯æ— 穷大,它是一个有é™å€¼ã€‚这个有é™åˆ¶ä¼šå¼•èµ·å®ƒçš„一个问题。本文è¦è®¨è®ºçš„å¦ä¸€ä¸ªé—®é¢˜æ˜¯å¢žç›Šå¸¦å®½ç§¯ï¼Œå…¶å®žæ›´æƒ³å¤šè¯´çš„一点是增益带宽的那æ¡æ›²çº¿ã€‚ 在ä¸å…·è´Ÿå馈情况下(开环路状况下),è¿ç®—放大器的放大å€æ•°ç§°ä¸ºå¼€çŽ¯å¢žç›Šï¼Œç®€ç§°AOL。这å¥è¯ç®€å•çš„定义了è¿æ”¾çš„开环增益。实际的è¿æ”¾çš„开环增益,有高有低,并且会éšæ¸©åº¦å˜åŒ–,这是我们ä¸æƒ³çœ‹åˆ°çš„。 先说说开环增益带æ¥çš„ä¸è‰¯å½±å“。开环增益为有é™å€¼çš„å处ä¸åªæ˜¯è¯´æ˜Žè¿æ”¾éƒ½ä¸æ˜¯ç†æƒ³çš„。它会带æ¥ä¸€ä¸ªå¸¸è¢«äººä»¬å¿½ç•¥çš„问题——误差。 下图是OPAl369çš„datasheetä¸ç»™å‡ºçš„关于开环增益的å‚æ•°ï¼Œé¦–å…ˆæ˜ å…¥çœ¼å¸˜ï¼ˆå°å¦ä½œæ–‡å¸¸ç”¨è¯ï¼‰çš„是开环增最典型值为134dB,最å°å€¼ä¸º114dB。这说明一点,åŒä¸€åž‹å·çš„一大批è¿æ”¾ï¼Œå®ƒä»¬å„自的开环增益是有一定分布的。 ç¬¬äºŒé¡¹æ˜ å…¥çœ¼å¸˜çš„æ˜¯è¿æ”¾çš„开环增益会éšæ¸©åº¦å˜åŒ–而å˜åŒ–。当然是å˜å了。在整个è¿æ”¾çš„使用范围里最å°å€¼å¯èƒ½è¾¾åˆ°90dB. 下é¢æˆ‘们计算一个Aol对放大电路的影å“。如下图是常è§çš„åŒç›¸æ¯”例放大电路。 如果考虑进Aol,则它的电压增益为 当å‡è®¾Avolä¸ºæ— ç©·å¤§æ—¶ï¼Œåˆ™ä¸Šè¿°æ”¾å¤§ç”µè·¯çš„å¢žç›ŠåŒ–ç®€ä¸º 误差为: 这个结果还ä¸é”™å·®ï¼Œç›¸å½“于20ppm的误差。 如果在宽温度范围下应用,最å情况呢, Bldc Motor,Brushless Dc Motor,Bldc Hub Motor,Brushless Dc Fan Wentelon Micro-Motor Co.,Ltd. , https://www.wentelon.com

Typically, an op amp's application circuit uses a linear power supply to power the op amp and filter the op amp's power supply. However, in some handheld devices, in order to improve efficiency and reduce power consumption, it is necessary to use a switching power supply to supply power to the operational amplifier. The frequency of the switching power supply often exceeds 100 kHz, even to the level of MHz. At this frequency point, the PSR capability of the op amp drops very quickly. If the OPA376 is at 100kHz, the PSRR is only 50dB. It is a far cry from DC-PSRR above 100dB. Another problem is that in a single-supply hand-held device, the "buck-boost" of the switched capacitor is often used to convert the positive supply to a negative supply. Seeing the AC-PSRR of the op amp on the negative power supply in the above picture will give us some cold sweat. The PSRR of the op amp is the change in the input offset voltage caused by the change in the supply voltage. Therefore, the PSRR can be measured by referring to the method of measuring the offset voltage. The PSRR can be calculated by changing the supply voltage by ⊿Vcc and then measuring ⊿Vios.

Typically, an op amp's application circuit uses a linear power supply to power the op amp and filter the op amp's power supply. However, in some handheld devices, in order to improve efficiency and reduce power consumption, it is necessary to use a switching power supply to supply power to the operational amplifier. The frequency of the switching power supply often exceeds 100 kHz, even to the level of MHz. At this frequency point, the PSR capability of the op amp drops very quickly. If the OPA376 is at 100kHz, the PSRR is only 50dB. It is a far cry from DC-PSRR above 100dB. Another problem is that in a single-supply hand-held device, the "buck-boost" of the switched capacitor is often used to convert the positive supply to a negative supply. Seeing the AC-PSRR of the op amp on the negative power supply in the above picture will give us some cold sweat. The PSRR of the op amp is the change in the input offset voltage caused by the change in the supply voltage. Therefore, the PSRR can be measured by referring to the method of measuring the offset voltage. The PSRR can be calculated by changing the supply voltage by ⊿Vcc and then measuring ⊿Vios.

Bias current ib offset current ios These op amp concepts have all understood?

A large number of op amp parameters are listed in the datasheet of the general op amp. Some are easy to understand, we are always concerned, and some may be ignored. In the next few topics, each parameter will be described and analyzed in detail. Try to clarify the parameters of the op amp on the principle and the impact on the application. Due to my limited level, it is inevitable that there will be some omissions in the written blog post. I hope everyone will criticize and correct.